- 您现在的位置:买卖IC网 > Sheet目录2010 > MAX5365EUT+T (Maxim Integrated Products)IC DAC 6BIT LP 3WIRE SER SOT23-6

MAX5363/MAX5364/MAX5365

Low-Cost, Low-Power, 6-Bit DACs with 3-Wire

Serial Interface in SOT23

_______________________________________________________________________________________

3

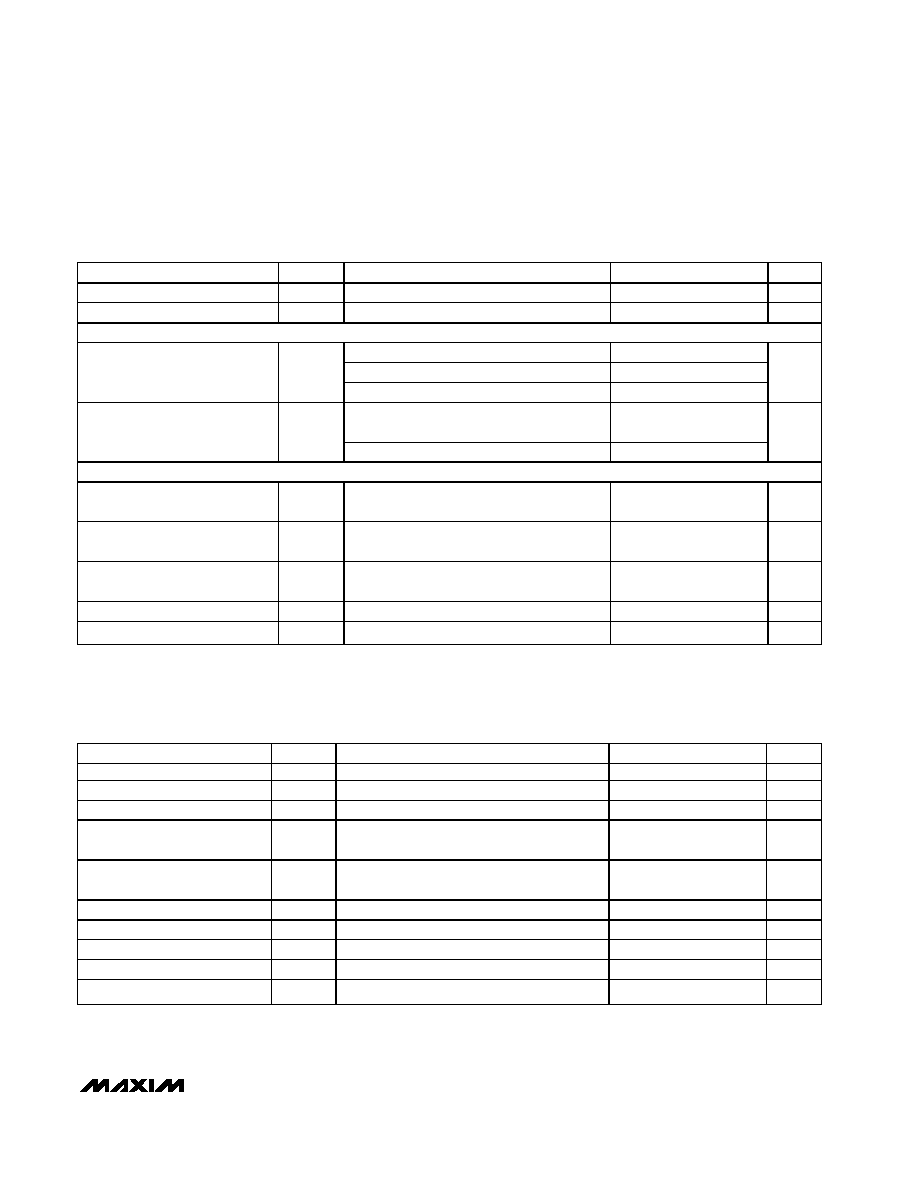

ELECTRICAL CHARACTERISTICS (continued)

(VDD = +2.7V to +3.6V (MAX5363), VDD = +4.5V to +5.5V (MAX5364), VDD = +2.7V to +5.5V (MAX5365), RL = 10k

, CL = 50pF, TA =

TMIN to TMAX, unless otherwise noted. Typical values are TA = +25°C.)

TIMING CHARACTERISTICS

(Figures 3 and 4, VDD = +2.7V to +3.6V (MAX5363), VDD = +4.5V to +5.5V (MAX5364), VDD = +2.7V to +5.5V (MAX5365), RL =

10k

, CL = 50pF, TA = TMIN to TMAX, unless otherwise noted. Typical values are TA = +25°C.) (Note 7)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Digital-Analog Glitch Impulse

Code 31 to code 32

40

nVs

Wake-Up Time

From software shutdown

50

s

POWER REQUIREMENTS

MAX5363

2.7

3.6

MAX5364

4.5

5.5

Supply Voltage

VDD

MAX5365

2.7

5.5

V

No load, all digital inputs at 0 or VDD,

code = 63

150

230

Supply Current

IDD

Shutdown mode

1

A

DIGITAL INPUTS

Input Low Voltage

VIL

0.3

×

VDD

V

Input High Voltage

VIH

0.7

×

VDD

V

Input Hysteresis

VH

0.05

×

VDD

V

Input Capacitance

CIN

(Note 7)

10

pF

Input Leakage Current

IIN

±1

A

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SCLK Period

tCP

100

ns

SCLK Pulse Width High

tCH

40

ns

SCLK Pulse Width Low

tCL

40

ns

CS Fall to SCLK Rise Setup

Time

tCSS

40

ns

SCLK Rise to

CS Rise Hold

Time

tCSH

0ns

DIN Setup Time

tDS

40

ns

DIN Hold Time

tDH

0ns

SCLK Rise to

CS Fall Delay

tCS0

10

ns

CS Rise to SCLK Rise Hold

tCS1

40

ns

CS Pulse Width High

tCSW

100

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX536BEWE+

IC DAC 12BIT QUAD CALIB 16-SOIC

MAX5380NEUK+T

IC DAC 8BIT 2WIRE SER SOT23-5

MAX5384EZT+T

IC DAC 8BIT 3WIRE SER TSOT23-6

MAX541AESA+

IC DAC 16BIT SER/VOLT I/O 8-SOIC

MAX5444AEUB+

IC DAC 16BIT 3V SERIAL 10-UMAX

MAX547BEMH+

IC DAC 13BIT OCTAL PAR 44-MQFP

MAX5480AEEE+T

IC DAC 8BIT PARALLEL 16-QSOP

MAX5511ETC+T

IC DAC 8BIT VOUT 12-TQFN-EP

相关代理商/技术参数

MAX5365EUT-T

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACPE

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACPE+

功能描述:数模转换器- DAC 12-Bit 4Ch Precision DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACWE

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACWE+

功能描述:数模转换器- DAC 12-Bit 4Ch Precision DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACWE+T

功能描述:数模转换器- DAC 12-Bit 4Ch Precision DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536ACWE-T

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX536AEPE

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube